1гҖҒеҺҹзҗҶз®Җд»Ӣ

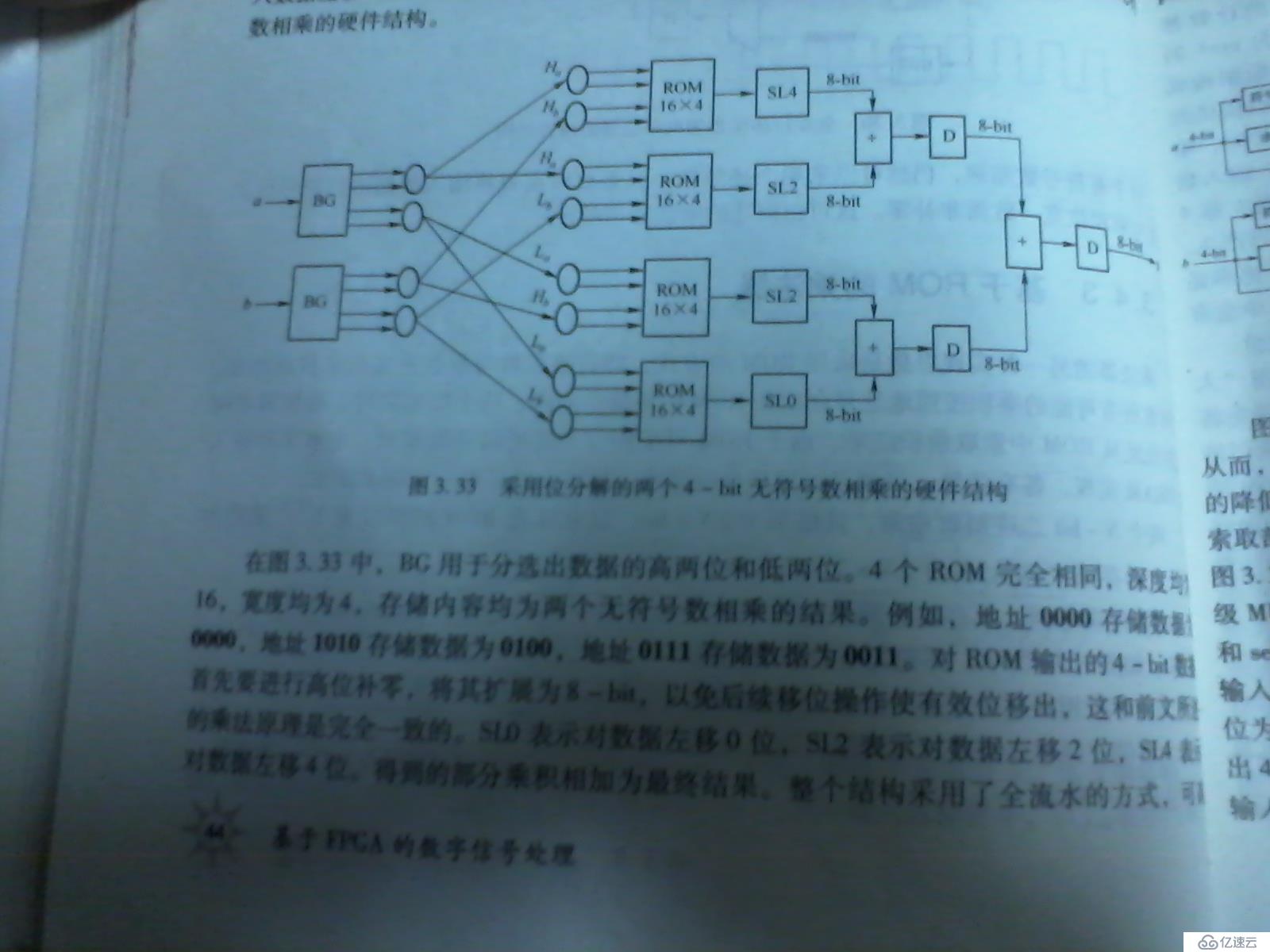

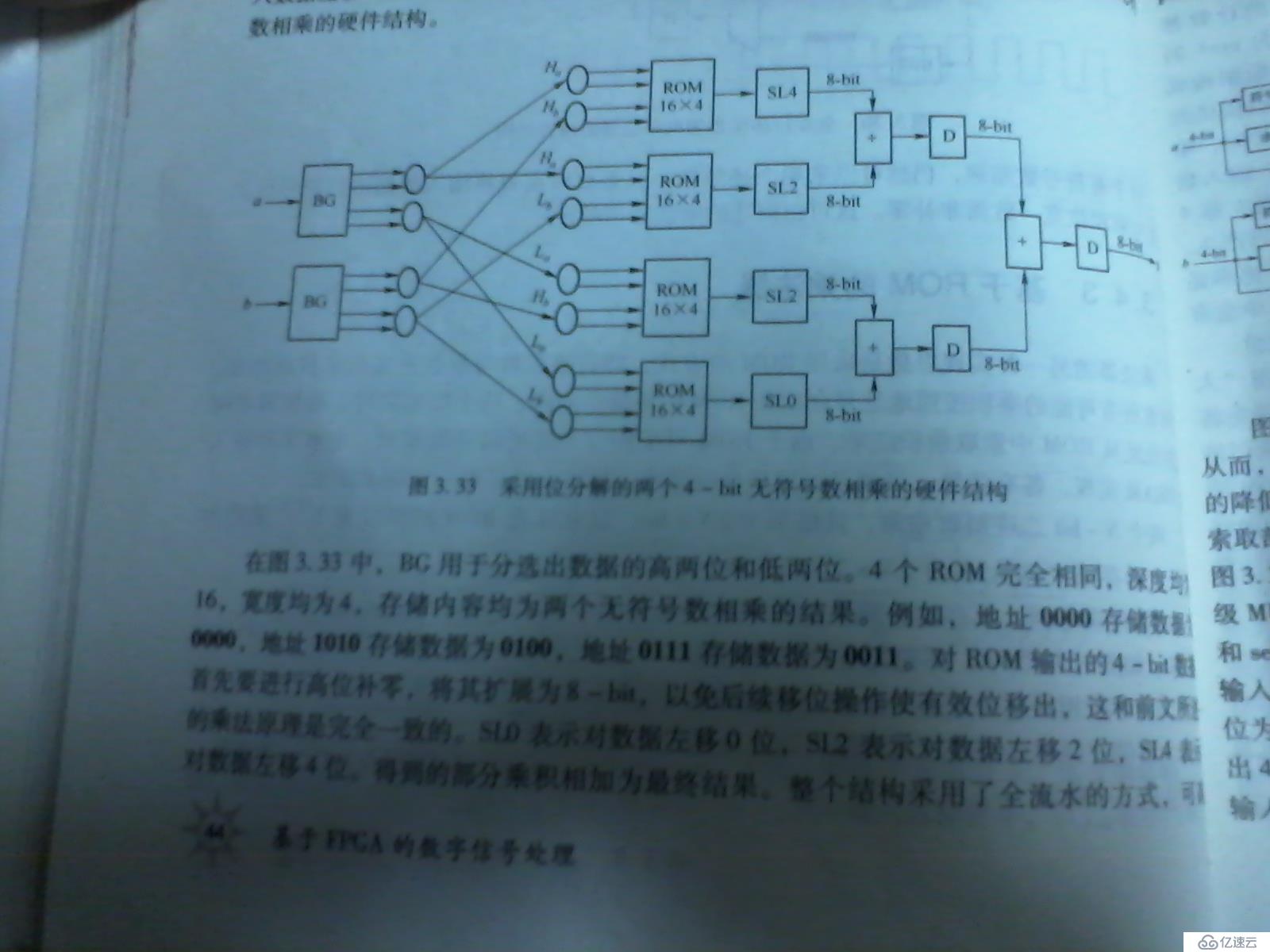

д№ҳжі•еҷЁзҡ„еҸҰдёҖз§Қе®һзҺ°жҖқжғіжҳҜйҮҮз”ЁROMзҡ„ж–№ејҸпјҢеҚіе°Ҷиў«д№ҳж•°е’Ңд№ҳж•°иҝһжҺҘиө·жқҘжӢјжҲҗең°еқҖпјҢжҠҠдёӨиҖ…жүҖжңүеҸҜиғҪзҡ„д№ҳз§ҜжҢүз…§ең°еқҖж”ҫеңЁROMзҡ„ең°еқҖз©әй—ҙдёӯпјҢдёӨдёӘж•°зӣёд№ҳж—¶пјҢж №жҚ®дёӨиҖ…жһ„жҲҗзҡ„ең°еқҖд»ҺROMдёӯиҜ»еҸ–д№ҳз§Ҝз»“жһңгҖӮROMеҸҜйҮҮз”ЁеҲҶеёғејҸйҖ»иҫ‘иө„жәҗе®һзҺ°пјҲз”ЁдәҺеӯҳеӮЁж•°жҚ®йҮҸе°Ҹзҡ„жғ…еҶөжҜ”иҫғеҗҲйҖӮпјүпјҢд№ҹеҸҜйҮҮз”ЁеөҢе…ҘејҸBRAMе®һзҺ°пјҲз”ЁдәҺеӯҳеӮЁйҮҸж•°жҚ®еӨ§зҡ„жғ…еҶөжҜ”иҫғеҗҲйҖӮпјүгҖӮ

дёӨдёӘN-bitзҡ„дәҢиҝӣеҲ¶ж•°зӣёд№ҳпјҢе…¶з»“жһңдёә2N-bitгҖӮиҝҷж„Ҹе‘ізқҖROMзҡ„ж·ұеәҰдёә2зҡ„2Nж¬Ўж–№пјҢе®ҪеәҰдёә2NгҖӮд»ҘдёӨдёӘ4-bitж•°зӣёд№ҳдёәдҫӢпјҢе…¶еӯҳеӮЁз©әй—ҙзҡ„еӨ§е°Ҹдёә256x8-bitпјҲ256дёәж·ұеәҰпјҢ8дёәе®ҪеәҰпјүпјҢжҳҫ然пјҢйҡҸзқҖдҪҚе®Ҫзҡ„еўһеҠ еӯҳеӮЁз©әй—ҙе°Ҷд»ҘжҢҮж•°йҖҹеәҰиҶЁиғҖгҖӮ

ж”№иҝӣж–№жі•пјҡе°Ҷиў«д№ҳж•°е’Ңд№ҳж•°иҝӣиЎҢдҪҚеҲҶи§ЈпјҢеҚіе°ҶеӨ§дҪҚе®Ҫзҡ„ж•°еҲҶи§ЈдёәеӨҡдёӘе°ҸдҪҚе®Ҫзҡ„ж•°жқҘеҲҶеҲ«зӣёд№ҳгҖӮдҫӢеҰӮдёӨдёӘ4-bitж•°зӣёд№ҳпјҢеҸҜе°Ҷ4-bitж•°еҲҶи§ЈжҲҗдёӨдёӘ2-bitж•°пјҢдёәдәҶдҝқиҜҒжңҖз»Ҳд№ҳз§Ҝз»“жһңзҡ„жӯЈзЎ®жҖ§пјҢйңҖиҰҒеҜ№дёӯй—ҙз»“жһңиҝӣиЎҢ移дҪҚгҖӮдёәж–№дҫҝиө·и§ҒпјҢд»ҘдёӨдёӘж— з¬ҰеҸ·дәҢиҝӣеҲ¶ж•°1101(еҜ№еә”еҚҒиҝӣеҲ¶дёә11)е’Ң0110пјҲеҜ№еә”еҚҒиҝӣеҲ¶ж•°дёә0110пјүзӣёд№ҳдёәдҫӢгҖӮе…¶зӣёд№ҳдҪҚеҲҶи§ЈеӨ„зҗҶжөҒзЁӢеҰӮдёӢеӣҫжүҖзӨәгҖӮ

йҮҮз”Ёзҡ„ROMж·ұеәҰдёә16пјҢе®ҪеәҰдёә4гҖӮеӯҳеӮЁзҡ„еҶ…е®№дёәдёӨдёӘж— з¬ҰеҸ·ж•°зӣёд№ҳзҡ„з»“жһңгҖӮең°еқҖеҸҠе…¶еҜ№еә”зҡ„еӯҳеӮЁеҶ…е®№еҰӮдёӢпјҡ

|

ең°еқҖ

|

0000

|

0001

|

0010

|

0011

|

0100

|

0101

|

0110

|

0111

|

1000

|

1001

|

1010

|

1011

|

1100

|

1101

|

1110

|

1111

|

|

еҶ…е®№(еҚҒиҝӣеҲ¶пјү

|

0

|

0

|

0

|

0

|

0

|

1

|

2

|

3

|

0

|

2

|

4

|

6

|

0

|

3

|

6

|

9

|

|

еҶ…е®№(еҚҒиҝӣеҲ¶пјү

|

0000

|

0000

|

0000

|

0000

|

0000

|

0001

|

0010

|

0011

|

0000

|

0010

|

0100

|

0110

|

0000

|

0011

|

0110

|

1001

|

2гҖҒverilogд»Јз Ғе®һзҺ°

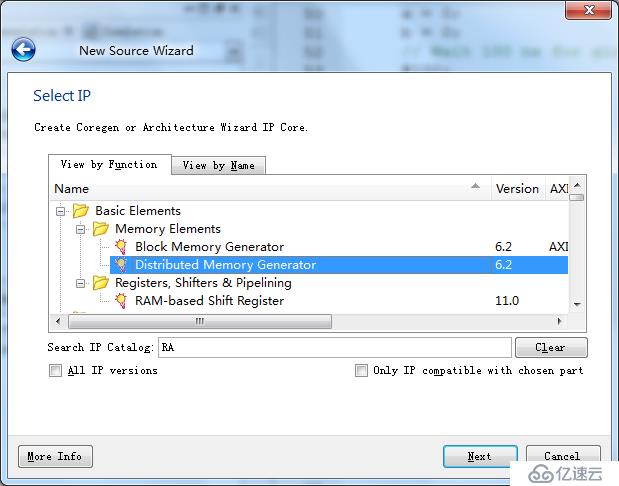

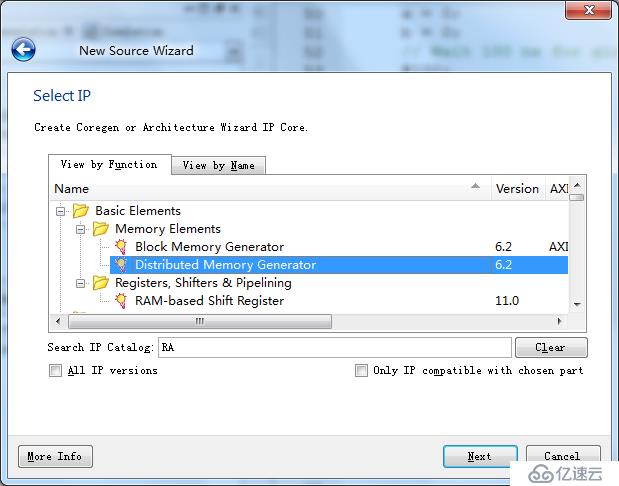

2.1иҠӮд»Ӣз»ҚROMдҪҝз”ЁDistributed Memory Generatorз”ҹжҲҗзҡ„IPж ёгҖӮ2.2иҠӮд»Ӣз»ҚдҪҝз”ЁXilinxеҺҹиҜӯз”ҹжҲҗзҡ„ROMпјҲе…¶е®һдҪҝз”Ёзҡ„д№ҹжҳҜеҲҶеёғејҸиө„жәҗпјүгҖӮBlock Memeory Generatorз”ҹжҲҗзҡ„IPж ёдҪҝз”Ёзҡ„жҳҜBlockRAMпјҢеҪ“еӯҳеӮЁеӨ§йҮҸж•°жҚ®ж—¶пјҢдҪҝз”ЁжҜ”иҫғж–№дҫҝпјҢе’ҢDistributed Memory Generatorзұ»дјјпјҢдёҚеҶҚиҜҰз»Ҷд»Ӣз»ҚгҖӮ

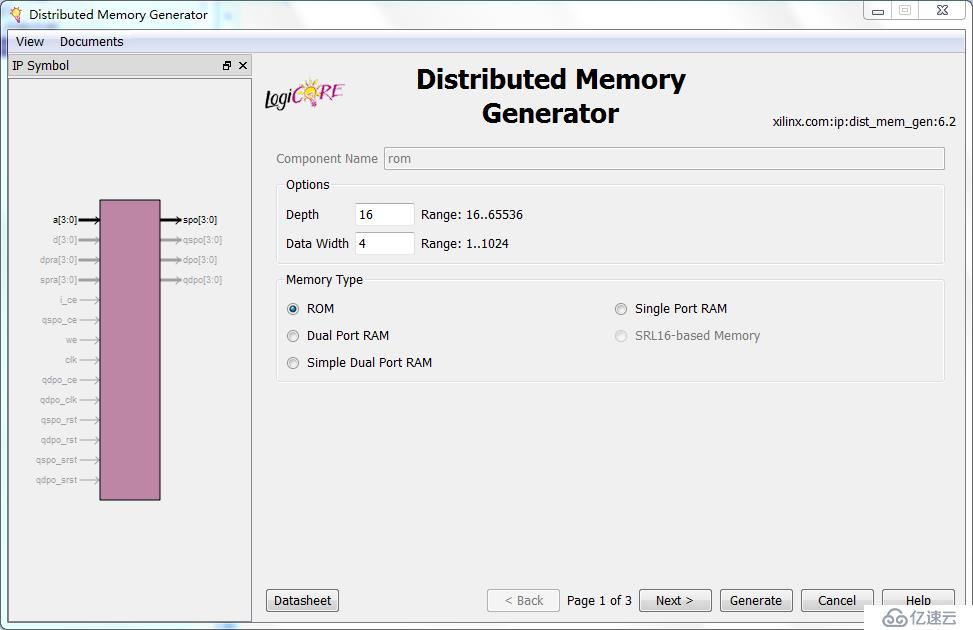

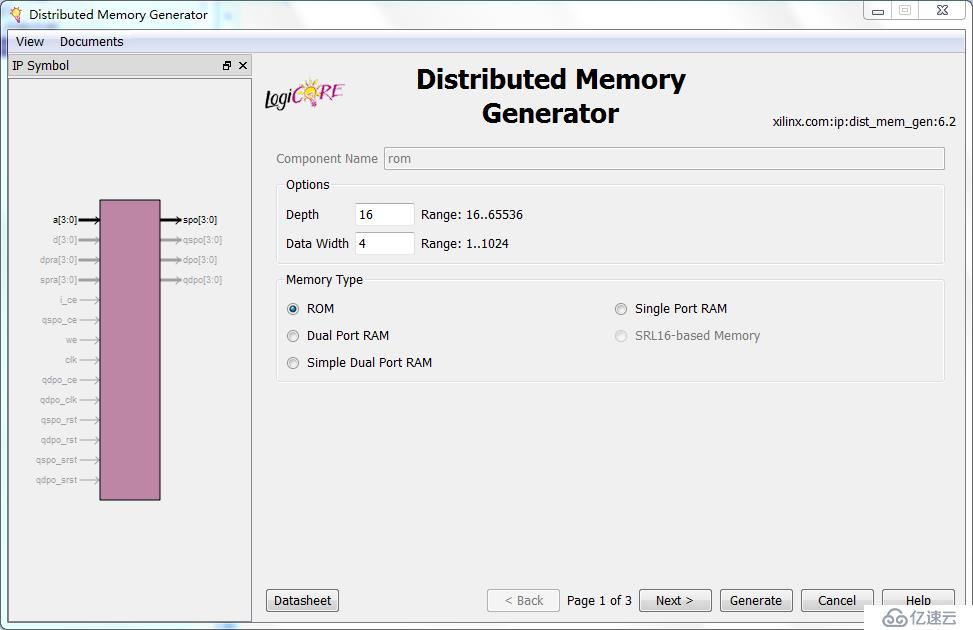

2.1 ROMйҮҮз”ЁеҲҶеёғејҸиө„жәҗз”ҹжҲҗзҡ„IPж ё

и®ҫзҪ®ROMзҡ„дҪҚе®ҪпјҢж·ұеәҰзӯүгҖӮ

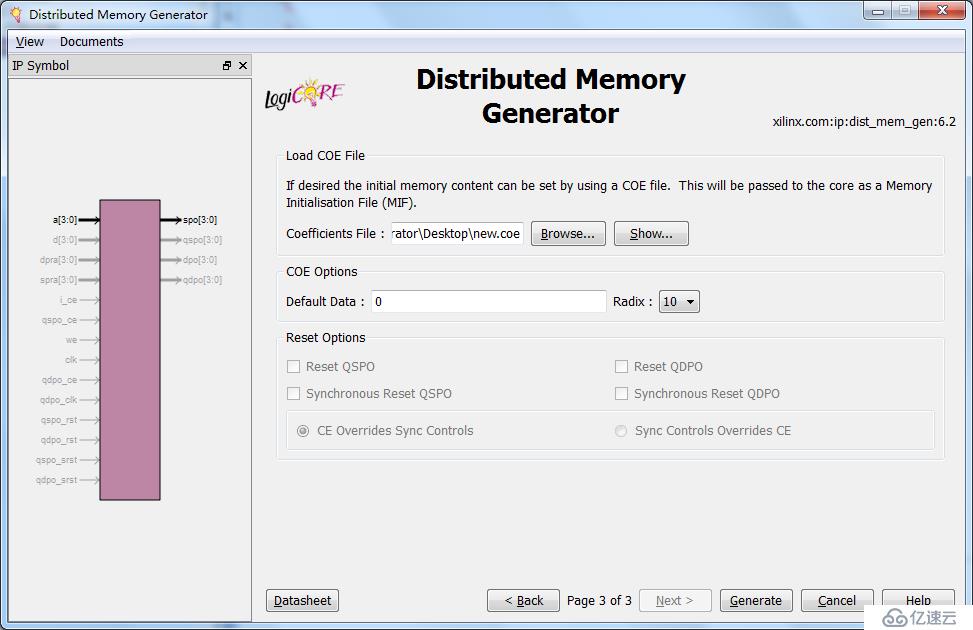

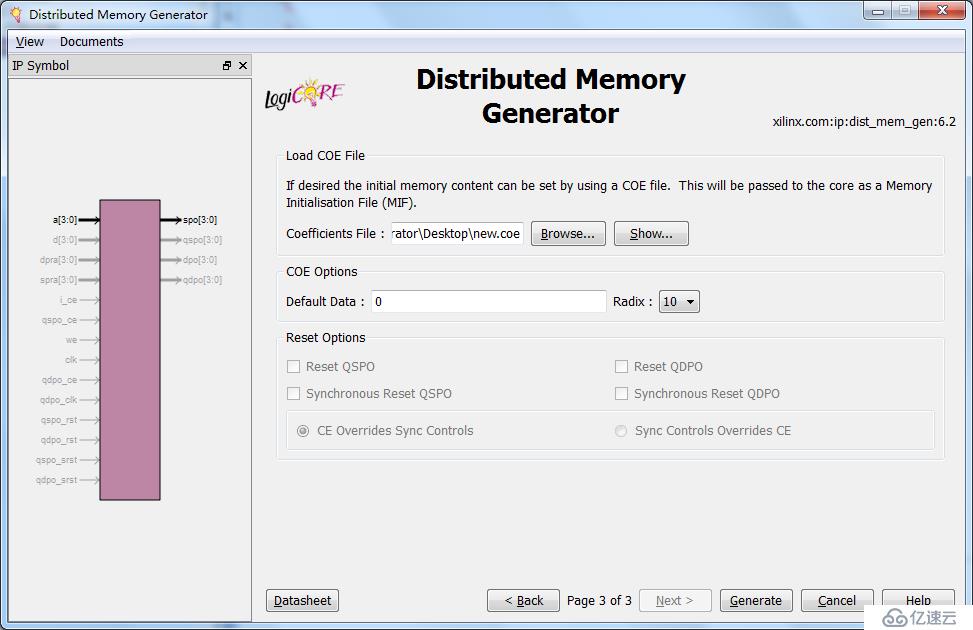

ROMиҝӣиЎҢеҲқе§ӢеҢ–пјҢйҮҮз”Ёcoeж–Ү件гҖӮ

coeж–Ү件зҡ„еҶ…е®№дёәпјҡ

MEMORY_INITIALIZATION_RADIX=10;

MEMORY_INITIALIZATION_VECTOR=

0,

0,

0,

0,

0,

1,

2,

3,

0,

2,

4,

6,

0,

3,

6,

9;

иҜҙжҳҺпјҡMEMORY_INITIALIZATION_RADIX=10пјҢиЎЁжҳҺдёӢйқўзҡ„ж•°жҚ®дёә10иҝӣеҲ¶пјҢиҝҳеҸҜд»ҘеҸ–еҖј2пјҢ8пјҢ16гҖӮ

MEMORY_INITIALIZATION_VECTOR=пјҢеҗҺйқўзҡ„еҶ…е®№дҫқж¬Ўдёәең°еқҖпјҲ0-15пјүжүҖеӯҳеӮЁзҡ„еҶ…е®№пјҢдёӯй—ҙз”ЁйҖ—еҸ·еҲҶйҡ”пјҢжңҖеҗҺз”ЁеҲҶеҸ·гҖӮ

жңҖеҗҺз”ҹжҲҗROMж ёгҖӮ

verilogд»Јз Ғе®һзҺ°

module rom_top(

input clk,

input rst_n,

input [3:0] a,

input [3:0] b,

output [7:0] c

);

wire [3:0] spo0,spo1,spo2,spo3;

wire [3:0] a0,a1,a2,a3;

assign a0={a[3:2],b[3:2]};

assign a1={a[3:2],b[1:0]};

assign a2={a[1:0],b[3:2]};

assign a3={a[1:0],b[1:0]};

reg [7:0] spo0_r,spo1_r,spo2_r,spo3_r;

always@(posedge clk) begin

if(!rst_n) begin

spo0_r<=0;spo1_r<=0;spo2_r<=0;spo3_r<=0;

end

else begin

spo0_r<={spo0,4'b0000};

spo1_r<={2'b00,spo1,2'b00};

spo2_r<={2'b00,spo2,2'b00};

spo3_r<={spo3};

end

end

assign c=(spo0_r+spo1_r)+(spo2_r+spo3_r);

// Instantiate the Unit Under Test (UUT)

rom uut0 ( //romдёәз”ҹжҲҗзҡ„IPж ё

.a(a0),

.spo(spo0)

);

rom uut1 (

.a(a1),

.spo(spo1)

);

rom uut2 (

.a(a2),

.spo(spo2)

);

rom uut3 (

.a(a3),

.spo(spo3)

);

endmodule

testbenchж–Ү件

module romtop_tb;

// Inputs

reg clk;

reg rst_n;

reg [3:0] a;

reg [3:0] b;

// Outputs

wire [7:0] c;

// Instantiate the Unit Under Test (UUT)

rom_top uut (

.clk(clk),

.rst_n(rst_n),

.a(a),

.b(b),

.c(c)

);

always #5 clk = ~clk;

initial begin

// Initialize Inputs

clk = 0;

rst_n = 0;

a = 0;

b = 0;

// Wait 100 ns for global reset to finish

#100;

rst_n=1;

#10;

#3;

a=2;b=6;

#10;

a=3;b=7;

#10;

a=15;b=9;

#10;

a=12;b=11;

#10;

a=6;b=7;

#100 $stop;

// Add stimulus here

end

endmodule

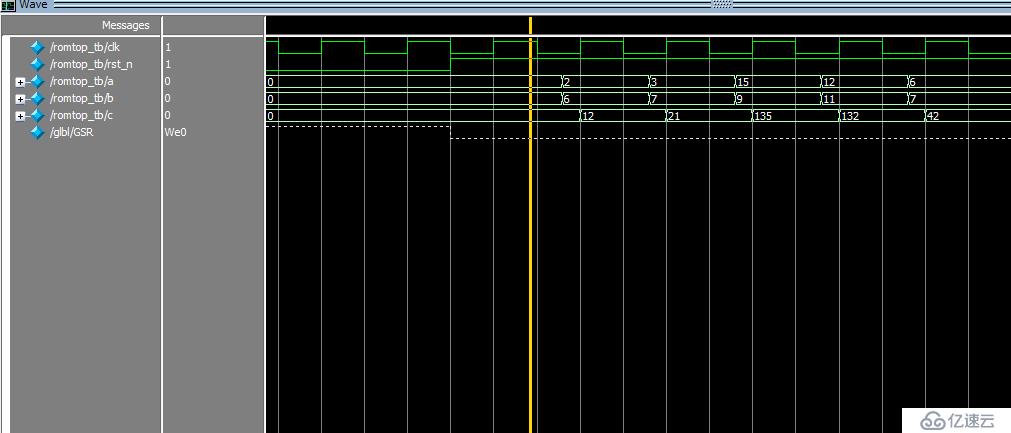

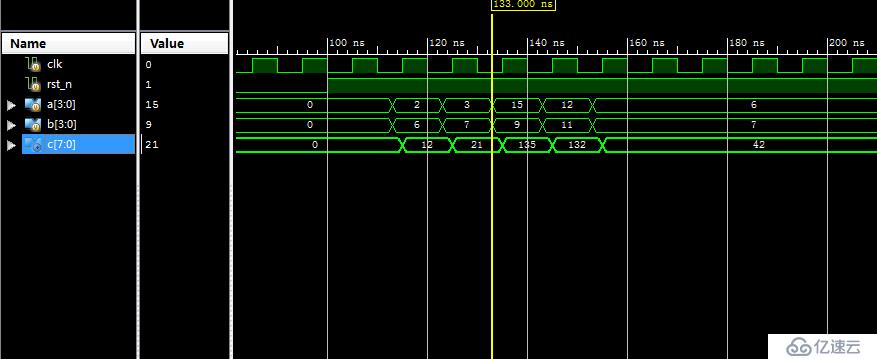

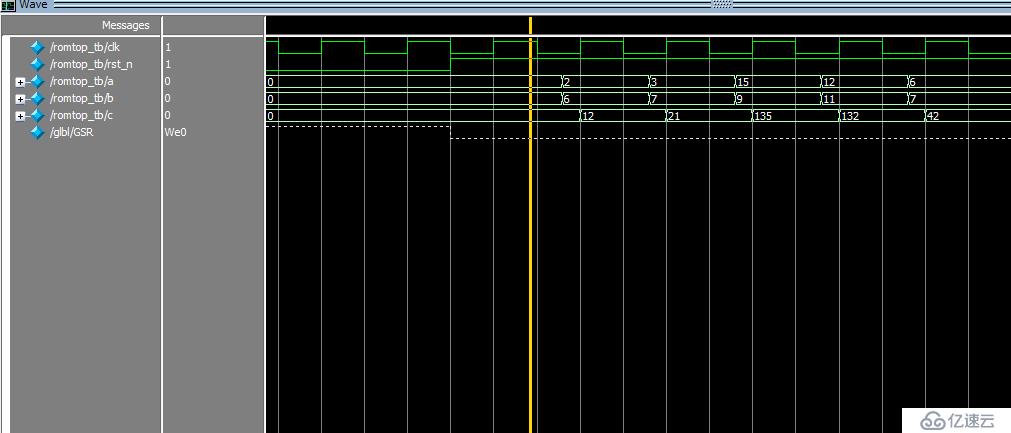

еңЁmodelsimдёӯд»ҝзңҹз”ҹжҲҗзҡ„жіўеҪўеӣҫпјҡaxb=c. 2x6=12 3x7=21 15x9=135

2.2 ROMйҮҮз”ЁXilinxеҺҹиҜӯз”ҹжҲҗ

verilogд»Јз Ғ

module d_rom_top(

input clk,

input rst_n,

input [3:0] a,

input [3:0] b,

output [7:0] c

);

wire [3:0] addra,addrb,addrc,addrd;

assign addra={a[3:2],b[3:2]};

assign addrb={a[3:2],b[1:0]};

assign addrc={a[1:0],b[3:2]};

assign addrd={a[1:0],b[1:0]};

wire [3:0] Oa,Ob,Oc,Od;

reg [7:0] Oa_r,Ob_r,Oc_r,Od_r;

always@(posedge clk)begin

if(!rst_n) begin

Oa_r<=0;Ob_r<=0;Oc_r<=0;Od_r<=0;

end

else begin

Oa_r<={Oa,4'b0000};

Ob_r<={2'b00,Ob,2'b00};

Oc_r<={2'b00,Oc,2'b00};

Od_r<={4'b0000,Od};

end

end

assign c=Oa_r+Ob_r+Oc_r+Od_r;

genvar i0,i1,i2,i3;

generate

for(i0=0;i0<4;i0=i0+1) begin :rom_unita

if(i0==0) begin

ROM16X1 #(.INIT(16'b1010_0000_1010_0000))

rom_0 (.O(Oa[0]),.A0(addra[0]),.A1(addra[1]),.A2(addra[2]),.A3(addra[3]));

end

else if(i0==1)begin

ROM16X1 #(.INIT(16'b0110_1010_1100_0000))

rom_1 (.O(Oa[1]),.A0(addra[0]),.A1(addra[1]),.A2(addra[2]),.A3(addra[3]));

end

else if(i0==2)begin

ROM16X1 #(.INIT(16'b0100_1100_0000_0000))

rom_2 (.O(Oa[2]),.A0(addra[0]),.A1(addra[1]),.A2(addra[2]),.A3(addra[3]));

end

else begin

ROM16X1 #(.INIT(16'b1000_0000_0000_0000))

rom_3 (.O(Oa[3]),.A0(addra[0]),.A1(addra[1]),.A2(addra[2]),.A3(addra[3]));

end

end

endgenerate

generate

for(i1=0;i1<4;i1=i1+1) begin :rom_unitb

if(i1==0) begin

ROM16X1 #(.INIT(16'b1010_0000_1010_0000))

rom_0 (.O(Ob[0]),.A0(addrb[0]),.A1(addrb[1]),.A2(addrb[2]),.A3(addrb[3]));

end

else if(i1==1)begin

ROM16X1 #(.INIT(16'b0110_1010_1100_0000))

rom_1 (.O(Ob[1]),.A0(addrb[0]),.A1(addrb[1]),.A2(addrb[2]),.A3(addrb[3]));

end

else if(i1==2)begin

ROM16X1 #(.INIT(16'b0100_1100_0000_0000))

rom_2 (.O(Ob[2]),.A0(addrb[0]),.A1(addrb[1]),.A2(addrb[2]),.A3(addrb[3]));

end

else begin

ROM16X1 #(.INIT(16'b1000_0000_0000_0000))

rom_3 (.O(Ob[3]),.A0(addrb[0]),.A1(addrb[1]),.A2(addrb[2]),.A3(addrb[3]));

end

end

endgenerate

generate

for(i2=0;i2<4;i2=i2+1) begin :rom_unitc

if(i2==0) begin

ROM16X1 #(.INIT(16'b1010_0000_1010_0000))

rom_0 (.O(Oc[0]),.A0(addrc[0]),.A1(addrc[1]),.A2(addrc[2]),.A3(addrc[3]));

end

else if(i2==1)begin

ROM16X1 #(.INIT(16'b0110_1010_1100_0000))

rom_1 (.O(Oc[1]),.A0(addrc[0]),.A1(addrc[1]),.A2(addrc[2]),.A3(addrc[3]));

end

else if(i2==2)begin

ROM16X1 #(.INIT(16'b0100_1100_0000_0000))

rom_2 (.O(Oc[2]),.A0(addrc[0]),.A1(addrc[1]),.A2(addrc[2]),.A3(addrc[3]));

end

else begin

ROM16X1 #(.INIT(16'b1000_0000_0000_0000))

rom_3 (.O(Oc[3]),.A0(addrc[0]),.A1(addrc[1]),.A2(addrc[2]),.A3(addrc[3]));

end

end

endgenerate

generate

for(i3=0;i3<4;i3=i3+1) begin :rom_unitd

if(i3==0) begin

ROM16X1 #(.INIT(16'b1010_0000_1010_0000))

rom_0 (.O(Od[0]),.A0(addrd[0]),.A1(addrd[1]),.A2(addrd[2]),.A3(addrd[3]));

end

else if(i3==1)begin

ROM16X1 #(.INIT(16'b0110_1010_1100_0000))

rom_1 (.O(Od[1]),.A0(addrd[0]),.A1(addrd[1]),.A2(addrd[2]),.A3(addrd[3]));

end

else if(i3==2)begin

ROM16X1 #(.INIT(16'b0100_1100_0000_0000))

rom_2 (.O(Od[2]),.A0(addrd[0]),.A1(addrd[1]),.A2(addrd[2]),.A3(addrd[3]));

end

else begin

ROM16X1 #(.INIT(16'b1000_0000_0000_0000))

rom_3 (.O(Od[3]),.A0(addrd[0]),.A1(addrd[1]),.A2(addrd[2]),.A3(addrd[3]));

end

end

endgenerate

endmodule

testbench:

module d_rom_top_tb;

// Inputs

reg clk;

reg rst_n;

reg [3:0] a;

reg [3:0] b;

// Outputs

wire [7:0] c;

// Instantiate the Unit Under Test (UUT)

d_rom_top uut (

.clk(clk),

.rst_n(rst_n),

.a(a),

.b(b),

.c(c)

);

always #5 clk=~clk;

initial begin

// Initialize Inputs

clk = 0;

rst_n = 0;

a = 0;

b = 0;

// Wait 100 ns for global reset to finish

#100;

rst_n=1;

#10;

#3;

a=2;b=6;

#10;

a=3;b=7;

#10;

a=15;b=9;

#10;

a=12;b=11;

#10;

a=6;b=7;

end

endmodule

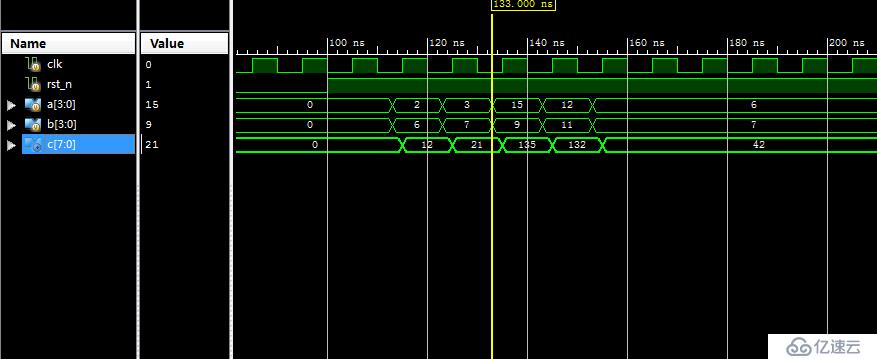

д»ҝзңҹеӣҫеҪўпјҡ

йҷ„件пјҡhttp://down.51cto.com/data/2362729