您好,登录后才能下订单哦!

今天我们来看看缓存。在我们平时的生活中,知道处理器和内存是不同的。它们所使用的半导体器件工艺不同,工艺的差异导致了处理器与内存的速度差异。处理器的器件比内存是要好很多的,因此它的容量就势必很小;而内存虽然速度慢,但是它很便宜,因此容量一般较大。在进行数据的处理时,处理器总是需要等待内存,处理器的速度是远远大于内存的。

在一般程序访问的时候,它会出现局部性的概念。也就是说,在短时间内,处理器访问的存储空间是一个很小的范围。局部性分为两种:时间局部性和空间局部性。局部时间性是指某个存储单元在短时间内很可能被再次访问,而空间局部性是指某个存储单元的邻近单元在短时间内也被访问。我们在处理器与内存之间就引进了一个中间介质,它叫高速缓冲存储器,俗称 cache。下来介绍下它的特性:1、cache 是一种小容量的高速存储器;2、cache 的存取速度与处理器的运算速度几乎同量级;3、cache 在现代计算机系统中内置于处理器芯片中。在处理器与内存之间设置 cache 能大大地提高效率,将内存中被频繁访问的指令和数据复制到 cache 中。在大多数情况下,处理器能直接从 cache 中取得指令和数据。

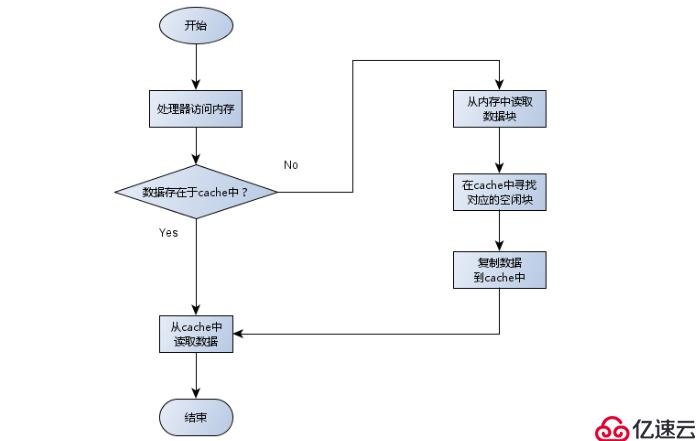

下来我们来看看处理器的数据访问 的具体流程,如下

那么内存和 cache 之间是如何进行映射的呢?是利用直接映射法的。1、将 cache 和内存分成固定大小的块(如 512 Byte/块);2、内存中的每一块在 cache 中有固定的映射位置;3、映射公式为:Pcache = 内存块号 % cache总块数。下图是一个直接映射的例子

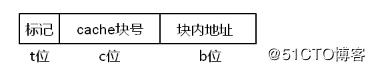

它的特点是任意一个内存地址都能映射到 cache 中的一个固定位置。它的地址划分如下

映射原理为根据访问地址的中间 c 位找到 cache 中的对应块,再来比较地址的高 t 位是否和 flag 相同,如果相同责直接读取数据,不相同的话则从内存中复制块内容。例如当前处理器需要访问内存地址为 0x02140CH 处。

1、地址划分:

| 0000 001 | 0010 | 0 0000 1100 |

2、根据 0010 直接访问 cache 中的第 0010 块

3、匹配 0010 块的 flag 是否等于 0000 001,如果相等则访问 0010 块中 1100 处的数据,不相等则从内存中读取块数据并更新 cache。

直接映射法的优点是映射过程简单,所需耗时短;而缺点是当短时间内访问的地址有同余冲突时会造成缓存失效。下面来看看基于 cache 原理的软件应用。项目背景是开发一款日志调试工具(Log Dog)。需要解决的问题是:1、日志对系统效率影响巨大,且不容易分析查看;2、现有的日志系统无法高效的打印二进制数据;3、自定义日志内容的解析方式;4、对日志进行分类,并控制日志是否输出。出现过的性能问题是当短时间内有大量日志需要打印时,性能无法满足调试需要。最终的解决方案是根据 cache 原理,设置二级缓存机制,尽量避开查找。

免责声明:本站发布的内容(图片、视频和文字)以原创、转载和分享为主,文章观点不代表本网站立场,如果涉及侵权请联系站长邮箱:is@yisu.com进行举报,并提供相关证据,一经查实,将立刻删除涉嫌侵权内容。