жӮЁеҘҪпјҢзҷ»еҪ•еҗҺжүҚиғҪдёӢи®ўеҚ•е“ҰпјҒ

1. VGAжҰӮиҝ°

VGA(Video Graphics Array)жҳҜIBMеңЁ1987е№ҙжҺЁеҮәзҡ„дёҖз§Қи§Ҷйў‘дј иҫ“пјҢе…·жңүеҲҶиҫЁзҺҮй«ҳгҖҒжҳҫзӨәйҖҹзҺҮеҝ«гҖҒйўңиүІдё°еҜҢзӯүдјҳзӮ№пјҢеңЁеҪ©иүІжҳҫзӨәеҷЁйўҶеҹҹеҫ—еҲ°дәҶе№ҝжіӣзҡ„еә”з”ЁгҖӮдёҚж”ҜжҢҒзғӯжҸ’жӢ”пјҢдёҚж”ҜжҢҒйҹійў‘дј иҫ“гҖӮ

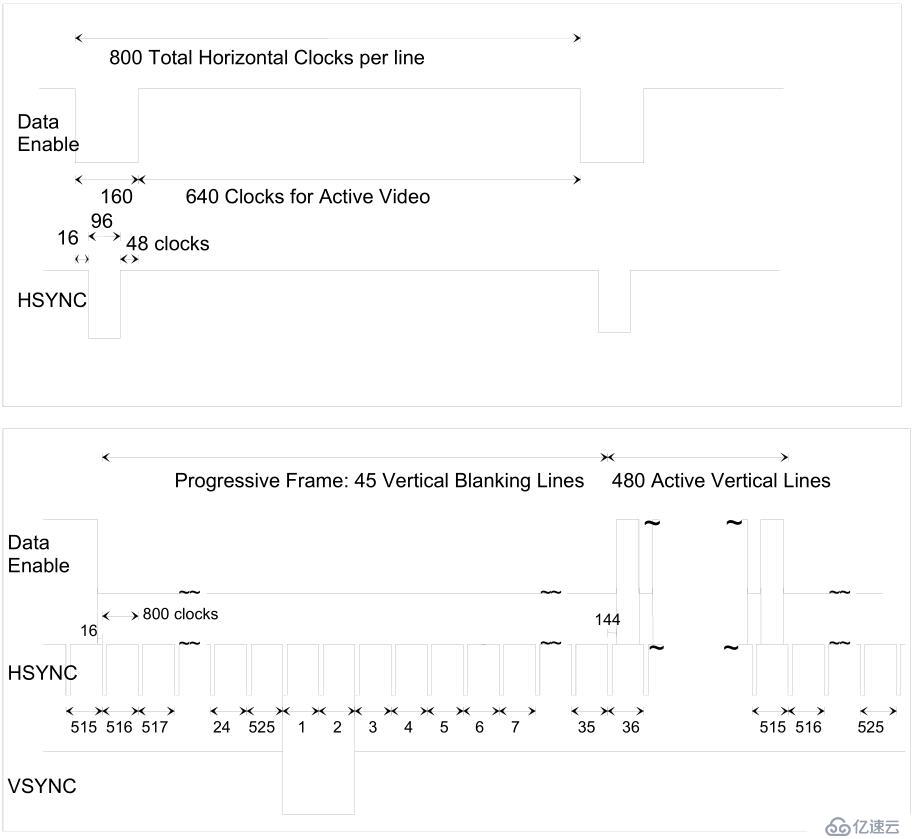

2. VGAж—¶еәҸ

дёӢйқўд»Ҙ640*480@60HzдёәдҫӢиҜҙжҳҺVGAж—¶еәҸе’ҢFPGAи®ҫи®ЎпјҢе…¶д»–еҲҶиҫЁзҺҮе’Ңеё§зҺҮзҡ„еҸҜеҸӮиҖғVESAдёӯжҹҘжүҫгҖӮ

и®Ўз®—еғҸзҙ ж—¶й’ҹpclk = 800*525*60 = 25200000пјҢжіЁж„ҸиҝҷйҮҢзҡ„HSYNCе’ҢVSYNCйғҪжҳҜдҪҺз”өе№іжңүж•ҲпјҢдё”HSYNCеңЁж•°жҚ®иЎҢж— ж•ҲеҢәеҹҹд№ҹиҰҒжҸҗдҫӣгҖӮ

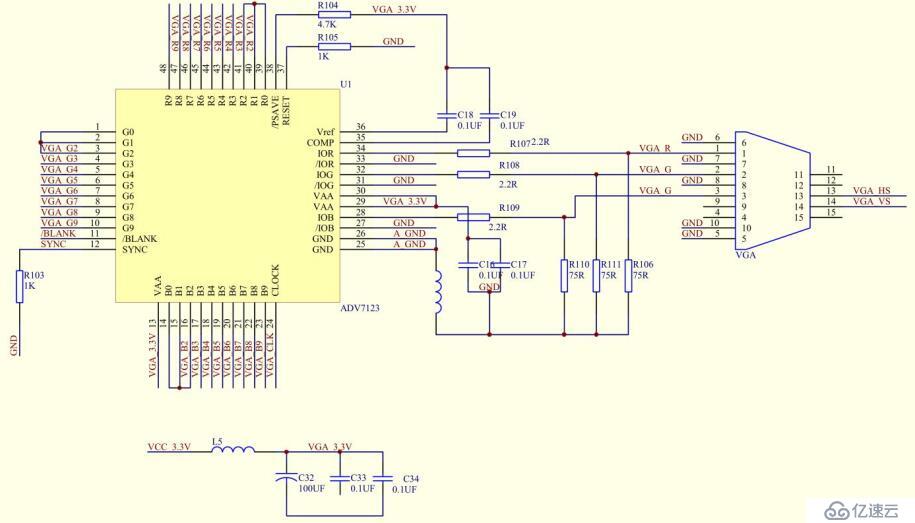

3. VGAз”өи·Ҝеӣҫ

з”өи·Ҝд»ҘADV7123дёәдҫӢпјҡ

4. FPGAйҖ»иҫ‘д»Јз Ғ

//------------Video Test--------------- parameter IMG_HDISP =16'd640; parameter IMG_VDISP = 16'd480; wire pclk; assign pclk = clk_25m; //VIDEO input reg [15:0] vcnt; reg [11:0] hcnt; reg vsync; reg hsync; reg [7:0] data; reg data_valid; always @(posedge pclk) if(hcnt>=(IMG_HDISP+159)) hcnt <= 0; else hcnt <= hcnt + 1'b1; always @(posedge pclk) if(hcnt>=(IMG_HDISP+159)) if(vcnt>=(IMG_VDISP+44)) vcnt <= 0; else vcnt <= vcnt + 1'b1; else vcnt <= vcnt; always @(posedge pclk) if((hcnt>=IMG_HDISP+16) & (hcnt<(IMG_HDISP+96)))// & (vcnt>=0) & (vcnt<(IMG_VDISP))) hsync <= 1'b1; else hsync <= 1'b0; always @(posedge pclk) if(vcnt>=(IMG_VDISP+9) & vcnt<(IMG_VDISP+11)) vsync <= 1'b1; else vsync <= 1'b0; always @(posedge pclk) if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=0) & (vcnt<(IMG_VDISP))) data_valid <= 1'b1; else data_valid <= 1'b0; always @(posedge pclk) if(vsync) data <= 0; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=0) & (vcnt<(IMG_VDISP/4))) // data <= data + 1'b1; if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'h00; else data <= 8'hff; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=(IMG_VDISP/4)) & (vcnt<(2*IMG_VDISP/4))) if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'hff; else data <= 8'h00; // data <= data + 1'b1; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=(2*IMG_VDISP/4)) & (vcnt<(3*IMG_VDISP/4))) if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'h00; else data <= 8'hff; // data <= data + 1'b1; else if((hcnt>=0) & (hcnt<(IMG_HDISP)) & (vcnt>=(3*IMG_VDISP/4)) & (vcnt<(IMG_VDISP))) // data <= data + 1'b1; if(hcnt>=0 & hcnt<(IMG_HDISP/4)) data <= 8'hff; else if(hcnt>=(IMG_HDISP/4) & hcnt<(2*IMG_HDISP/4)) data <= 8'h00; else if(hcnt>=(2*IMG_HDISP/4) & hcnt<(3*IMG_HDISP/4)) data <= 8'hff; else data <= 8'h00; else data <= 0; assign lcd_vs = ~vsync; assign lcd_hs = ~hsync; assign vga_red = data; assign vga_green = data; assign vga_blue = data; assign lcd_dclk = clk_25m; assign lcd_blank = 1'b1; assign lcd_sync = 1'b0; wire [7:0] vga_red; wire [7:0] vga_green; wire [7:0] vga_blue; assign lcd_red[9:2] = vga_red; assign lcd_green[9:2] = vga_green; assign lcd_blue[9:2] = vga_blue;

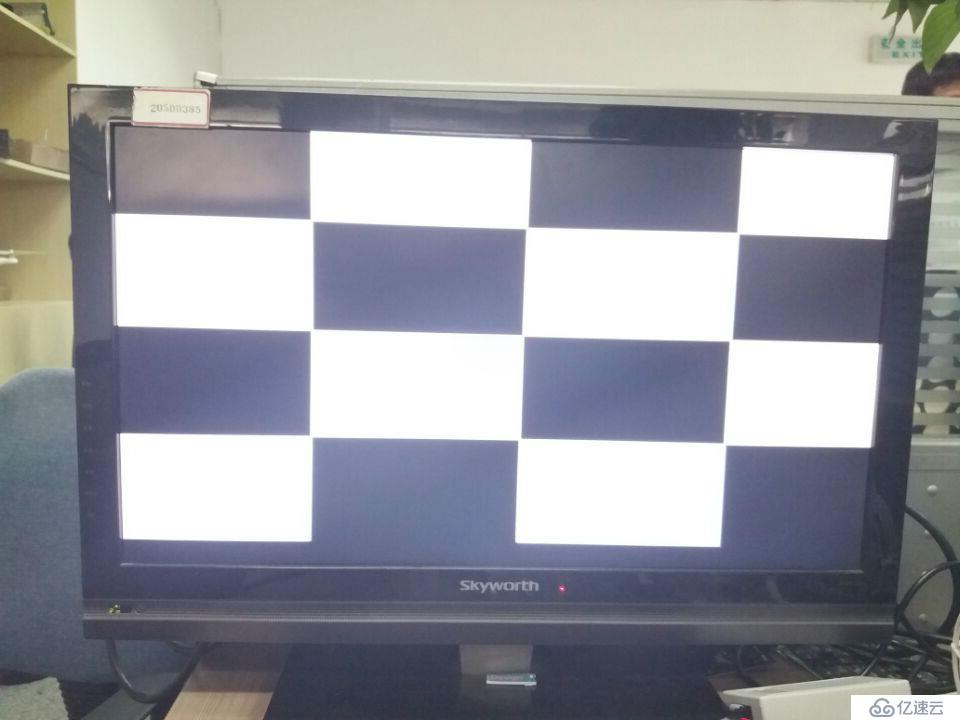

5.жј”зӨәз»“жһң

дёӢеӣҫдёәж–№ж јжҳҫзӨәж•Ҳжһңпјҡ

е…ҚиҙЈеЈ°жҳҺпјҡжң¬з«ҷеҸ‘еёғзҡ„еҶ…е®№пјҲеӣҫзүҮгҖҒи§Ҷйў‘е’Ңж–Үеӯ—пјүд»ҘеҺҹеҲӣгҖҒиҪ¬иҪҪе’ҢеҲҶдә«дёәдё»пјҢж–Үз« и§ӮзӮ№дёҚд»ЈиЎЁжң¬зҪ‘з«ҷз«ӢеңәпјҢеҰӮжһңж¶үеҸҠдҫөжқғиҜ·иҒ”зі»з«ҷй•ҝйӮ®з®ұпјҡis@yisu.comиҝӣиЎҢдёҫжҠҘпјҢ并жҸҗдҫӣзӣёе…іиҜҒжҚ®пјҢдёҖз»ҸжҹҘе®һпјҢе°Ҷз«ӢеҲ»еҲ йҷӨж¶үе«ҢдҫөжқғеҶ…е®№гҖӮ

жӮЁеҘҪпјҢзҷ»еҪ•еҗҺжүҚиғҪдёӢи®ўеҚ•е“ҰпјҒ